# PPC/PowerCoreCPCI-6750 Reference Guide

P/N 211344 Revision AC August 2002

# Copyright

The information in this publication is subject to change without notice. Force Computers, GmbH reserves the right to make changes without notice to this, or any of its products, to improve reliability, performance, or design.

Force Computers, GmbH shall not be liable for technical or editorial errors or omissions contained herein, nor for indirect, special, incidental, or consequential damages resulting from the furnishing, performance, or use of this material. This information is provided "as is" and Force Computers, GmbH expressly disclaims any and all warranties, express, implied, statutory, or otherwise, including without limitation, any express, statutory, or implied warranty of merchantability, fitness for a particular purpose, or non-infringement.

This publication contains information protected by copyright. This publication shall not be reproduced, transmitted, or stored in a retrieval system, nor its contents used for any purpose, without the prior written consent of Force Computers, GmbH.

Force Computers, GmbH assumes no responsibility for the use of any circuitry other than circuitry that is part of a product of Force Computers, GmbH. Force Computers, GmbH does not convey to the purchaser of the product described herein any license under the patent rights of Force Computers, GmbH nor the rights of others.

Copyright© 2002 by Force Computers, GmbH. All rights reserved.

The Force logo is a trademark of Force Computers, GmbH.

IEEE is a registered trademark of the Institute for Electrical and Electronics Engineers, Inc.

PICMG, CompactPCI, and the CompactPCI logo are registered trademarks and the PICMG logo is a trademark of the PCI Industrial Computer Manufacturer's Group.

MS-DOS, Windows95, Windows98, Windows2000 and Windows NT are registered trademarks and the logos are a trademark of the Microsoft Corporation.

Intel and Pentium are registered trademarks and the Intel logo is a trademark of the Intel Corporation.

SPARC is a registered trademark and the SPARC logo is a trademark of SPARC International, Inc.

PowerPC is a registered trademark and the PowerPC logo is a trademark of International Business Machines Corporation. AltiVec is a registered trademark and the AltiVec logo is a trademark of Motorola, Inc.

Other product names mentioned herein may be trademarks and/or registered trademarks of their respective companies.

#### World Wide Web: www.forcecomputers.com

24-hour access to on-line manuals, driver updates, and application notes is provided via SMART, our SolutionsPLUS customer support program that provides current technical and services information.

# **Headquarters**

### **The Americas**

**Force Computers Inc.** 4305 Cushing Parkway Fremont, CA 94538 U.S.A.

Tel.: +1 (510) 445-6000 Fax: +1 (510) 445-6001 Email: support@fci.com

### Europe

Force Computers GmbH Lilienthalstr. 15 D-85579 Neubiberg/München Germany

Tel.: +49 (89) 608 14-0 Fax: +49 (89) 609 77 93 Email: support-de@fci.com

### Asia

Force Computers Japan KK Shibadaimon MF Building 4F 2-1-16 Shiba Daimon Minato-ku, Tokyo 105-0012 Japan

Tel.: +81 (03) 3437 6221 Fax: +81 (03) 3437 6223 Email: support-de@fci.com

# **Table of Contents**

### **Using This Manual**

**Safety Notes**

Sicherheitshinweise

| 1 | Intro | duction                                            |                                                   |  |

|---|-------|----------------------------------------------------|---------------------------------------------------|--|

|   | 1.1   | Specifi                                            | cation                                            |  |

|   | 1.2   | Produ                                              | ct Nomenclature                                   |  |

|   | 1.3   | Orderi                                             | ing Information                                   |  |

| 2 | Insta | llation                                            |                                                   |  |

|   | 2.1   | Install                                            | ation Prerequisites and Requirements5             |  |

|   |       | 2.1.1                                              | Requirements                                      |  |

|   |       | 2.1.2                                              | Terminal Connection                               |  |

|   |       | 2.1.3                                              | Location Overview                                 |  |

|   |       | 2.1.4                                              | Upgrading the PPC/PowerCoreCPCI-6750 10           |  |

|   | 2.2   | Install                                            | ing Under Hot-Swap Conditions 10                  |  |

|   | 2.3   | Autom                                              | atic Power Up – Voltage Sensor and Watchdog Timer |  |

|   | 2.4   | Switch                                             | Settings                                          |  |

|   | 2.5   | Front Panel                                        |                                                   |  |

|   | 2.6   | PPC/PowerCoreCPCI-6750 Parameters and Timers – CIO |                                                   |  |

|   | 2.7   | Serial                                             | I/O Ports                                         |  |

|   | 2.8   | PCI-to                                             | -ISA Interface                                    |  |

|   | 2.9   | Ethernet Interface                                 |                                                   |  |

|   | 2.10  | CompactPCI Interface                               |                                                   |  |

|   | 2.11  | Compa                                              | actPCI Connector Pinout                           |  |

|   |       | -                                                  |                                                   |  |

|   | 2.12 | PMC S                | lots                                              |  |

|---|------|----------------------|---------------------------------------------------|--|

|   |      | 2.12.1               | PMC Voltage Keys                                  |  |

|   |      | 2.12.2               | Connector Configuration                           |  |

|   |      | 2.12.3               | ISA Connector                                     |  |

|   | 2.13 | Testing              | the Board Using PowerBoot                         |  |

| 3 | Hard | lware                |                                                   |  |

|   | 3.1  | PPC/Po               | owerCoreCPCI-6750 Address Map                     |  |

|   | 3.2  | PPC/Po               | owerCoreCPCI-6750 Interrupt Map34                 |  |

|   | 3.3  | 3.3 Hot-Swap Support |                                                   |  |

|   | 3.4  | PowerF               | PC CPU                                            |  |

|   | 3.5  | L2 Cac               | he                                                |  |

|   | 3.6  | Shared               | Memory                                            |  |

|   |      | 3.6.1                | Memory Controller                                 |  |

|   |      | 3.6.2                | Shared Memory Performance                         |  |

|   |      | 3.6.3                | Shared Memory Capacity                            |  |

|   |      | 3.6.4                | Shared Memory Organization                        |  |

|   |      | 3.6.5                | Cache Coherency and Snooping                      |  |

|   |      | 3.6.6                | Shared Memory Access from the PowerPC CPU         |  |

|   |      | 3.6.7                | Shared Memory Access via the CompactPCI Bus       |  |

|   |      | 3.6.8                | Shared Memory Access from the Ethernet Controller |  |

|   |      | 3.6.9                | Shared Memory Access from the PMC Modules         |  |

|   |      | 3.6.10               | Shared Memory Access from the PCI-to-ISA Bridge   |  |

|   | 3.7  | Boot Fl              | ash                                               |  |

|   |      | 3.7.1                | Boot Flash Address Range                          |  |

|   |      | 3.7.2                | Boot Flash Size and Address Map 48                |  |

|   |      | 3.7.3                | Boot Flash Devices                                |  |

|   |      | 3.7.4                | Programming the Boot Flash                        |  |

|   | 3.8  | User Fl              | ash                                               |  |

|   |      | 3.8.1                | User Flash Address Range                          |  |

|   |      | 3.8.2                | User Flash Size                                   |  |

|   |      | 3.8.3                | User Flash Devices                                |  |

|   |      | 3.8.4                | Programming the User Flash                        |  |

| ompactPCI Bus Interface       58         ocal PCI Bus Interface       59         acception Signals       60         hernet Controller       61         hernet Interface Adapter       62         Bridge       62         Cl-to-ISA Function       63         cl-torUler.       63         Clock / Non-Volatile RAM.       65         *CoreCPCI-6750 Parameters, Timers, and CIO       66 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bcal PCI Bus Interface 59   acception Signals 60   aterface 60   hernet Controller 61   hernet Interface Adapter 62   Bridge 62   CI-to-ISA Function 63   terrupt Controller. 63   Clock / Non-Volatile RAM. 65   *CoreCPCI-6750 Parameters, Timers, and CIO 66                                                                                                                          |

| Acception Signals60Iterface60hernet Controller61hernet Interface Adapter62Bridge62CI-to-ISA Function63terrupt Controller63Clock / Non-Volatile RAM65COreCPCI-6750 Parameters, Timers, and CIO66                                                                                                                                                                                          |

| Atterface       60         hernet Controller       61         hernet Interface Adapter       62         Bridge       62         CI-to-ISA Function       63         terrupt Controller       63         Clock / Non-Volatile RAM       65         *CoreCPCI-6750 Parameters, Timers, and CIO       66                                                                                    |

| hernet Controller. 61<br>hernet Interface Adapter . 62<br>Bridge . 62<br>CI-to-ISA Function . 63<br>terrupt Controller. 63<br>Clock / Non-Volatile RAM. 65<br>CoreCPCI-6750 Parameters, Timers, and CIO . 66                                                                                                                                                                             |

| hernet Interface Adapter                                                                                                                                                                                                                                                                                                                                                                 |

| Bridge    62      CI-to-ISA Function    63      terrupt Controller.    63      Clock / Non-Volatile RAM.    65      *CoreCPCI-6750 Parameters, Timers, and CIO    66                                                                                                                                                                                                                     |

| CI-to-ISA Function       63         terrupt Controller.       63         Clock / Non-Volatile RAM.       65         CoreCPCI-6750 Parameters, Timers, and CIO       66                                                                                                                                                                                                                   |

| terrupt Controller                                                                                                                                                                                                                                                                                                                                                                       |

| CI-to-ISA Function63terrupt Controller.63Clock / Non-Volatile RAM.65CoreCPCI-6750 Parameters, Timers, and CIO66rameters66                                                                                                                                                                                                                                                                |

| Clock / Non-Volatile RAM                                                                                                                                                                                                                                                                                                                                                                 |

| CoreCPCI-6750 Parameters, Timers, and CIO66                                                                                                                                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                          |

| rameters                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                          |

| mers                                                                                                                                                                                                                                                                                                                                                                                     |

| O                                                                                                                                                                                                                                                                                                                                                                                        |

| O: Port A Data Register                                                                                                                                                                                                                                                                                                                                                                  |

| O: Port B Data Register                                                                                                                                                                                                                                                                                                                                                                  |

| O: Port C Data Register                                                                                                                                                                                                                                                                                                                                                                  |

| us and Capability Registers - BSCRs69                                                                                                                                                                                                                                                                                                                                                    |

| SCR: Watchdog Timer 1 Sanity Check Register                                                                                                                                                                                                                                                                                                                                              |

| SCR: Watchdog Timer 2 Sanity Check Register                                                                                                                                                                                                                                                                                                                                              |

| SCR: Watchdog Status Register                                                                                                                                                                                                                                                                                                                                                            |

| SCR: Last Reset Register                                                                                                                                                                                                                                                                                                                                                                 |

| SCR: Reset Request Register                                                                                                                                                                                                                                                                                                                                                              |

| Ports – SCCs                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                                          |

4

| 5 | Pow | erBoot fo | or PPC/PowerCoreCPCI-675081        |

|---|-----|-----------|------------------------------------|

|   | 5.1 | PPC/P     | owerCoreCPCI-6750 Address Map82    |

|   | 5.2 | РМСР      | CI – Mapping PMC Modules           |

|   | 5.3 | RESE      | Γ – Restarting the Board85         |

|   | 5.4 | SETB(     | DOT – Editing Auto Boot Parameters |

|   | 5.5 | USERI     | LED – Setting User LED             |

|   | 5.6 | Flash N   | Memory                             |

|   |     | 5.6.1     | Boot Flash                         |

|   |     | 5.6.2     | User Flash                         |

## **Product Error Report**

Tab./Fig.

Page

# List of Tables and Figures

| History of Manual Publicationix                                                               | Tab.         | а        |

|-----------------------------------------------------------------------------------------------|--------------|----------|

| Fonts, Notations and Conventionsix                                                            | Tab.         | b        |

| Specification of the PPC/PowerCoreCPCI-6750                                                   | Tab.         | 1        |

| Nomenclature of the PPC/PowerCoreCPCI-6750                                                    | Tab.         | 2        |

| Excerpt from the Product's Ordering Information                                               | Tab.         | 3        |

| Typical Power Requirements of the Board incl. Memory Module                                   | Tab.         | 4        |

| Qualified Memory Module configurations                                                        | Tab.         | 5        |

| Max. Power Consumption of the Upper Memory Modules                                            | Tab.         | 6        |

| Environmental Requirements of the PPC/PowerCoreCPCI-6750                                      | Tab.         | 7        |

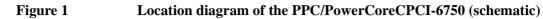

| Location diagram of the PPC/PowerCoreCPCI-6750 (schematic)                                    | Fig.         | 1        |

| Default Switch Settings                                                                       | Tab.         | 8        |

| Front-panel Features                                                                          | Tab.         | 9        |

| Pinout of the Front-Panel Serial I/O Ports for RS-232 17                                      | Tab.         | 10       |

| 8-pin RJ-45 Connector                                                                         | Tab.         | 11       |

| Pinout of the CompactPCI Connector J4, Rows AE                                                | Fig.         | 2        |

| Pinout of the CompactPCI Connector J5, Rows AE                                                | Fig.         | 3        |

| PN15 Connector Pinout                                                                         | Fig.         | 4        |

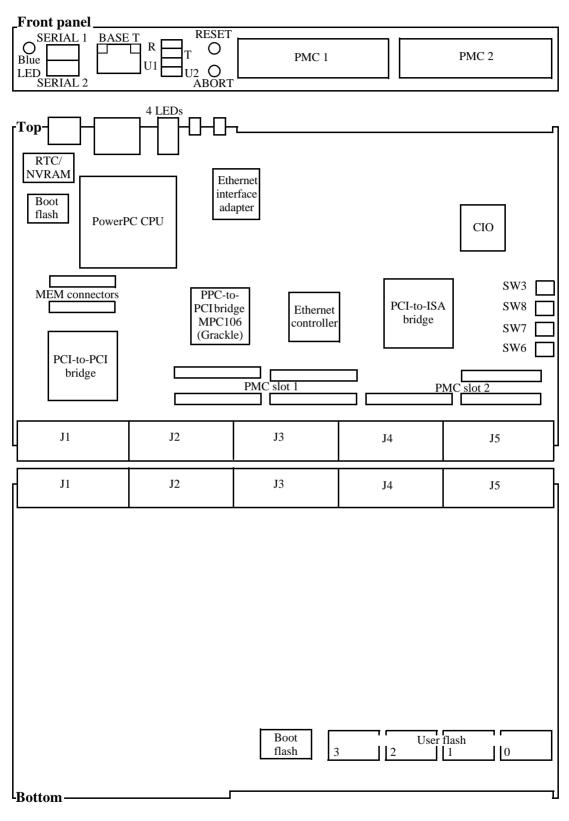

| PPC/PowerCoreCPCI-6750 Block Diagram                                                          | Fig.         | 5        |

| Buses, Busmodes, and Connected Devices                                                        | Tab.         | 12       |

| Bus Frequencies                                                                               | Tab.         | 13       |

| PPC/PowerCoreCPCI-6750 Memory Map seen from the CPU                                           | Tab.         | 14       |

| PPC/PowerCoreCPCI-6750 Memory Map seen from the PCI                                           | Tab.         | 15       |

| PPC/PowerCoreCPCI-6750 I/O Map seen from the PCI                                              | Tab.         | 16       |

| PPC/PowerCoreCPCI-6750Configuration Base Addresses                                            | Tab.         | 17       |

| PPC/PowerCoreCPCI-6750 ISA Bus Ports seen from the CPU                                        | Tab.         | 18       |

| PPC/PowerCoreCPCI-6750 PCI I/O Devices seen from the CPU                                      | Tab.         | 19       |

| Default PPC/PowerCoreCPCI-6750 Interrupt Map                                                  | Tab.         | 20       |

| PMC Interrupt Routing                                                                         | Tab.         | 21       |

| Hot-swap Control and Status Register, Bits [76], [3], and [1]                                 | Tab.         | 22       |

| DCCR, Bits [76]                                                                               | Tab.         | 23       |

| DCCR, Bits [50]                                                                               | Tab.         | 24       |

| EDO DRAM Capacity                                                                             | Tab.         | 25       |

| SDRAM Capacity                                                                                | Tab.         | 26       |

| Default Shared Memory Access from the PowerPC CPU                                             | Tab.         | 27       |

| CIO: Port A Data Register, bit [54]                                                           | Tab.         | 28       |

| Boot Flash Address Range                                                                      | Tab.         | 29       |

| Boot Flash Address Map49Boot Flash Factory Options, Device Types, and Default Configuration49 | Tab.         | 30<br>21 |

|                                                                                               | Tab.<br>Tab. | 31<br>32 |

| CIO: Port A Data Register, Bits [30] 51                                                       | 1 au.        | 34       |

| Page                                                         | Tab./Fig. |

|--------------------------------------------------------------|-----------|

| User Alash Address Map 51                                    | Tab. 33   |

| User Alash Address Range                                     | Tab. 34   |

| User Flash Device Types (Factory Options) and Address Ranges | Tab. 35   |

| CIO: port A Data Register, Bit [7] 54                        | Tab. 36   |

| BSCR: Watchdog Status Register, Bits [40]                    | Tab. 37   |

| CAR and CDR address map 57                                   | Tab. 38   |

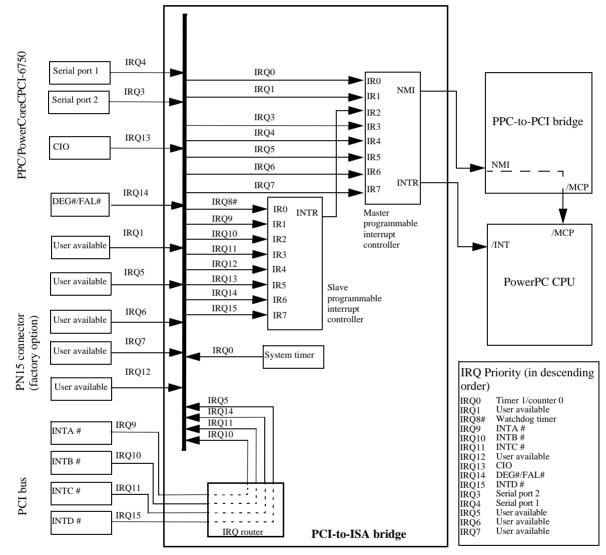

| Default PCI-to-ISA Bridge Interrupt Structure                | Fig. 6    |

| Address Ranges of the RTC/NVRAM                              | Tab. 39   |

| CIO: Port A Data Register                                    | Tab. 40   |

| CIO: Port B Data Register, Bits [76]                         | Tab. 41   |

| CIO: Port C Data Register, Bits [30]                         | Tab. 42   |

| BSCR: Watchdog Timer 1 Sanity Check Register, Bits [70] 69   | Tab. 43   |

| BSCR: Watchdog Timer 2 Sanity Check Register, Bits [70]      | Tab. 44   |

| BSCR: Watchdog Status Register, Bits [40]                    | Tab. 45   |

| BSCR: Last Reset Register, Bits [75] and [20]                | Tab. 46   |

| BSCR: Reset Request Register, Bits [70]                      | Tab. 47   |

| SCC Base Addresses                                           | Tab. 48   |

| CIO: Port B Data Register, Bits [51]                         | Tab. 49   |

| CIO: Port B Data Register, Bit [0]                           | Tab. 50   |

| PPC/PowerCoreCPCI-6750 Address Map Seen from the CPU         | Tab. 51   |

| PCI Addressing Spaces                                        | Tab. 52   |

| PCI I/O Addressing Spaces of the SCSI Controllers            | Tab. 53   |

# **Using This Manual**

This section does not provide information on the product but on common features of the manual itself:

- its structure,

- special layout conventions,

- and related documents.

#### Audience of the Technical Reference Manual

The *Technical Reference Manual* is intended for hard- and software developers installing and integrating the PPC/PowerCoreCPCI-6750 into their systems.

#### **Overview of the Technical Reference Manual**

The *Technical Reference Manual* additionally includes the *PowerBoot User's Manual*.

The *Technical Reference Manual* provides a comprehensive hardware and software guide to the board.

#### IMPORTANT

Please take a moment to examine the "Table of Contents" of the *Technical Reference Manual* to see how this documentation is structured. This will be of value to you when looking for information in the future.

Technical Reference Manual The Technical Reference Manual includes:

- a brief overview of the product, the specifications, and the ordering information: see section 1 "Introduction" on page 1.

- the installation instructions for powering up the board: see section 3 "Installation" on page 9. It includes the default configuration (switches and the like), initialization, and connector pinouts.

The installation instructions also appear as the product's installation guide – a separate manual delivered together with each shipped product.

• a detailed hardware description: see section 3 "Hardware" on page 25.

• a description of the board specific PowerBoot commands: see section 5 "PowerBoot for PPC/PowerCoreCPCI-6750" on page 81.

PowerBootThe PowerBoot User's Manual describes only those PowerBoot com-<br/>mands which are independent of the board. The board specific Power-<br/>Boot commands are described in the Technical Reference Manual (see<br/>section 5 "PowerBoot for PPC/PowerCoreCPCI-6750" on page 81).<br/>The PowerBoot User's Manual is packaged separately and always<br/>shipped together with the Technical Reference Manual.

Insert the *PowerBoot User's Manual* now: see section 4 "PowerBoot (= PowerBoot User's Manual)".

### **Publication History of the Manual**

#### Table a

| History | of Manual Pub | olication |

|---------|---------------|-----------|

|---------|---------------|-----------|

| Edition/<br>Revision | Date          | Description                                                                                                                                                                                                                    |

|----------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0                  | July 1998     | First print                                                                                                                                                                                                                    |

| 1.1                  | December 1998 | Excerpt from the data sheet's or-<br>dering information updated, pow-<br>er requirements and bus<br>frequencies of the 300-MHz and<br>400-MHz boards included,<br>SETBOOT corrected, flash mem-<br>ory programming exemplified |

| 2.0                  | April 1999    | Edition increased to archive Rev. 1                                                                                                                                                                                            |

| 3.0                  | April 1999    | PPC/PowerCoreCPCI-6750 Rev. 2                                                                                                                                                                                                  |

| AA                   | November 2000 | Added safety notes; editorial changes; removed data sheets                                                                                                                                                                     |

| AB                   | August 2001   | Added chapter Sicherheitshinweise                                                                                                                                                                                              |

| AC                   | August 2002   | Editorial changes                                                                                                                                                                                                              |

### Fonts, Notations and Conventions

#### Table b

#### Fonts, Notations and Conventions

| Notation                | Description                                                                                                                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0000.0000 <sub>16</sub> | Typical notation for hexadecimal numbers (digits are 0 through F), e.g. used for addresses and offsets.<br>Note the dot marking the 4th (to its right) and 5th (to its left) digit.          |

| 00008                   | Same for octal numbers (digits are 0 through 7)                                                                                                                                              |

| 00002                   | Same for binary numbers (digits are 0 and 1)                                                                                                                                                 |

| Program                 | Typical character format used for names, values, and<br>the like that should be used typing literally the same<br>word. Also used for on-screen-output.                                      |

| Variable                | Typical character format for words that represent a<br>part of a command, a programming statement, or the<br>like and that will be replaced by an applicable value<br>when actually applied. |

#### Table b

Fonts, Notations and Conventions (cont.)

| Notation | Description                                                                                                                                                                                                      |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| #        | A # symbol at the end of a PCI, ISA, or IDE signal<br>name indicates that the signal is active when it is at<br>low voltage. The absence of the # symbol indicates<br>that the signal is active at high voltage. |

| *        | A * symbol at the end of a VMEbus signal name indi-<br>cates that the signal is active when it is at low voltage.<br>The absence of the * symbol indicates that the signal<br>is active at high voltage.         |

Register Conventions Force Computers assumes that the software developer initializes the register bits which are not described with default settings.

#### Icons for Ease of Use: Safety Notes and Tips & Tricks

There are 3 levels of safety notes used in this manual which are described in short in the following subsections by displaying a typical layout example.

Be sure, to always read and follow the safety notes of a section first – before acting as documented in the other parts of the section.

Dangerous situation: injuries to people or severe damage to objects possible.

Possibly dangerous situation: no injuries to people but damage to objects possible.

No danger encountered. Only application hints and time-saving tips & tricks or information on typical errors when using the information mentioned below this safety hint.

# **Safety Notes**

This section provides safety precautions to follow when installing, operating, and maintaining the PPC/PowerCoreCPCI-6750. For your protection, follow all warnings and instructions found in the following text. This Technical Reference Manual provides the necessary information to install and handle the PPC/PowerCoreCPCI-6750. As the product is complex and its usage manifold, we do not guarantee that the given information is complete. If you need additional information, ask your Force Computers representative.

The PPC/PowerCoreCPCI-6750 has been designed to meet the standard industrial safety requirements. It must not be used except in its specific area of office telecommunication industry and industrial control.

Only personnel trained by Force Computers or persons qualified in electronics or electrical engineering are authorized to install, uninstall or maintain the PPC/PowerCoreCPCI-6750. The information given in this manual is meant to complete the knowledge of a specialist and must not be taken as replacement for qualified personnel.

EMC

The board has been tested in a Standard Force Computers system and found to comply with the limits for a Class A digital device in this system, pursuant to part 15 of the FCC Rules respectively EN 55022 Class A.

These limits are designed to provide reasonable protection against harmful interference when the system is operated in a commercial environment.

The board generates, uses and can radiate radio frequency energy and, if not installed properly and used in accordance with this Technical Reference Manual, may cause harmful interference to radio communications. Operating the system in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

If boards are integrated into open systems, always cover empty slots.

To ensure proper EMC shielding, always operate the PPC/PowerCoreCPCI-6750 with the blind panels or with PMC modules installed.

## Installation

|           | Electrostatic discharge and incorrect board installation and uninstal-<br>lation can damage circuits or shorten their life. Therefore:                                                                                                        |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | <ul> <li>Before installing or uninstalling the board, check the "Require-<br/>ments" section on page -5.</li> </ul>                                                                                                                           |

|           | <ul> <li>Before touching integrated circuits, make sure that you are work-<br/>ing in an ESD-safe environment.</li> </ul>                                                                                                                     |

|           | <ul> <li>When plugging the board in or removing it, do not press on the<br/>front panel but use the handles.</li> </ul>                                                                                                                       |

|           | <ul> <li>Before installing or uninstalling an additional device or module,<br/>read the respective documentation.</li> </ul>                                                                                                                  |

|           | <ul> <li>Make sure that the board is connected to the CompactPCI back-<br/>plane via all assembled connectors and that power is available on<br/>all power pins.</li> </ul>                                                                   |

| Operation |                                                                                                                                                                                                                                               |

|           | While operating the board ensure that the environmental and power requirements are met.                                                                                                                                                       |

|           | When operating the board in areas of strong electromagnetic radia-<br>tion ensure that the board is bolted on the CompactPCI rack and shielded by enclosure.                                                                                  |

|           | Make sure that contacts and cables of the board cannot be touched while the board is operating.                                                                                                                                               |

| Hot Swap  |                                                                                                                                                                                                                                               |

|           | Never install or uninstall the board in a system under hot-swap con-<br>ditions unless the basic hot-swap, full hot swap or high-availability<br>platform is used and the system documentation explicitly includes<br>appropriate guidelines. |

| Expansion |                                                                                                                                                                                                                                               |

|           | Check the total power consumption of all components installed (see<br>the technical specification of the respective components).                                                                                                              |

|           |                                                                                                                                                                                                                                               |

Ensure that any individual output current of any source stays within its acceptable limits (see the technical specification of the respective source).

Only replace components or system parts with those recommended by Force Computers. Otherwise, you are fully responsible for the impact on EMI and the possibly changed functionality of the product.

### **RJ-45** Connector

An RJ-45 connector is used for both telephone and twisted pair Ethernet (TPE) connectors. Mismatching the two connectors may destroy your telephone as well as your PPC/PowerCoreCPCI-6750. Therefore:

- TPE connectors near your working area have to be clearly marked as network connectors.

- TPE bushing of the system has to be connected only to safety extra low voltages (SELV) circuits.

- The length of the electric cable connected to a TPE bushing must not exceed 100 meter.

#### **Battery**

If a Lithium battery on the board has to be exchanged, observe the following safety notes:

- Incorrect exchange of Lithium batteries can result in a hazardous explosion.

- Always use the same type of Lithium battery as is already installed.

#### Environment

Always dispose of used batteries and/or old boards according to your country's legislation.

# Sicherheitshinweise

Dieser Abschnitt enthält Sicherheitshinweise, welche bei der Installation, dem Betrieb und der Wartung des PPC/PowerCoreCPCI-6750 zu beachten sind. Beachten Sie zu Ihrem Schutz alle folgenden Warnhinweise und Anleitungen.

Dieses Installationshandbuch enthält alle notwendigen Informationen zur Installation und zum Betrieb des PPC/PowerCoreCPCI-6750. Da es sich um ein komplexes Produkt mit einer aufwendigen Bedienung handelt, kann keine Garantie dafür übernommen werden, dass die enthaltenen Informationen vollständig sind. Für weitere Informationen wenden Sie sich bitte an Ihren Vertreter der Firma Force Computers.

Das PPC/PowerCoreCPCI-6750 erfüllt die gültigen industriellen Sicherheitsanforderungen. Dieses Produkt darf ausschließlich für Anwendungen innerhalb der Telekommunikationsindustrie und der industriellen Steuerung verwendet werden.

Lediglich von Force Computers eingewiesene oder im Bereich Elektrotechnik oder Elektronik qualifizierte Personen sind zur Installation, zum Betrieb und zur Wartung dieses Produktes befugt. Die in dieser Dokumentation enthaltenen Informationen sollen lediglich als Hilfestellung für entsprechend qualifiziertes Fachpersonal dienen. Keinesfalls kann es dieses ersetzen.

### EMV

Das Board wurde in einem Force Computers Standardsystem getestet und entspricht den Grenzen eines Klasse-A-Produktes gemäß Abschnitt 15 der FCC-Richtlinien, insbesondere EN 55022 Klasse A.

Diese Grenzen sind dafür vorgesehen, einen vernünftigen Schutz gegen störende Einflüsse bei einem Betrieb in einer kommerziellen Umgebung zu gewährleisten.

Das Board erzeugt elektromagnetische Strahlung. Wird das System un-sachgemäß installiert oder in anderer Weise als in diesem Installationshandbuch beschrieben betrieben, kann es in der Umgebung von Rundfunksendern und in Wohngegenden zu Störungen kommen. In diesem Fall ist der Benutzer verpflichtet, entstehende Störungen auf seine Kosten beheben zu lassen und die Kosten von Messungen selbst zu tragen.

Werden Boards in offene Systeme eingebaut, müssen freie Steckplätze mit einer Blende abgeschirmt werden. Um eine ausreichende Abschirmung zu gewährleisten, darf das Board nur mit einer Blindblende oder mit einer installierten PMC-Karte betrieben werden.

### Installation

|          | Elektrostatische Entladung und unsachgemäße Installation und Ausbau des<br>Boards kann Schaltkreise beschädigen oder ihre Lebensdauer verkürzen.<br>Deswegen sind folgende Punkte vor der Installation zu überprüfen:                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | • Lesen Sie vor Einbau oder Ausbau des Boards den Abschnitt "Requir-<br>ments" auf Seite 5.                                                                                                                                                                                                                                              |

|          | • Bevor Sie integrierte Schaltkreise berühren, vergewissern Sie sich, dass Sie in einem ESD-geschützten Bereich arbeiten.                                                                                                                                                                                                                |

|          | • Drücken Sie beim Einbau oder Ausbau des Boards nicht auf das Front Panel, sondern benutzen Sie die Griffe.                                                                                                                                                                                                                             |

|          | • Lesen Sie vor dem Einbau oder Ausbau von zusätzlichen Geräten oder<br>Modulen das jeweilige Benutzerhandbuch.                                                                                                                                                                                                                          |

|          | • Vergewissern Sie sich, dass das Board über alle Stecker an die Compact-<br>PCI Backplane angeschlossen ist und Strom an allen Power Pins anliegt.                                                                                                                                                                                      |

| Betrieb  |                                                                                                                                                                                                                                                                                                                                          |

|          | Während des Betriebs müssen die Umgebungs- und die Stromsversorgungsbe-<br>dingungen gewährleistet sein.                                                                                                                                                                                                                                 |

|          | Wenn das Board in Gebieten mit starker elektromagnetischer Strahlung<br>betrieben wird, stellen Sie sicher, dass das Board auf dem Compact PCI Rack<br>verschraubt ist und mit einem Gehäuse geschützt ist.                                                                                                                              |

|          | Es ist sicherzustellen, dass Anschlüsse und Kabel des Boards während des<br>Betriebs nicht versehentlich berührt werden können.                                                                                                                                                                                                          |

| Hot Swap |                                                                                                                                                                                                                                                                                                                                          |

|          | Einbau oder Ausbau des Boards in einem System unter Hot Swap Bedingun-<br>gen darf nur dann stattfinden, wenn die grundlegende Hot Swap Plattform,<br>die vollständige Hot Swap Plattform, oder die Hochverfügbarkeits Hot Swap<br>Plattform benutzt wird und die Systembeschreibung ausdrücklich die<br>geeigneten Richtlinien vorgibt. |

Beachten Sie den Gesamtstromverbrauch aller installierter Komponenten (siehe technische Daten der entsprechenden Komponente).

Vergewissern Sie sich, daß jeder individuelle Ausgangsstrom jedes Stromverbrauchers innerhalb der zulässigen Grenzwerte liegt (siehe technische Daten des entsprechenden Verbrauchers).

Benutzen Sie bei der Erweiterung ausschließlich von Force Computers empfohlene Komponenten und Systemteile. Ansonsten sind Sie für die Auswirkungen auf EMV und die möglicherweise geänderte Funktionalität des Produktes verantwortlich.

### **RJ-45 Stecker**

RJ-45 Stecker werden sowohl für Telefonanschlüsse als auch für Twistedpair-Ethernet (TPE) verwendet. Die Verwechslung solcher Anschlüsse kann sowohl das Telefonsystem als auch das Board zerstören. Daher:

- TPE-Anschlüsse in der Nähe Ihres Arbeitsplatzes müssen deutlich als Netzwerkanschlüsse gekennzeichnet sein.

- An TPE-Buchsen dürfen nur SELV-Kreise angeschlossen werden (Sicherheitskleinspannungsstromkreise).

- Die Länge der an einer TPE-Buchse angeschlossenen Leitung darf nicht mehr als 100 Meter betragen.

### Batterie

Muss eine Lithium Batterie auf dem Board ausgetauscht werden, müssen die folgenden Sicherheitshinweise beachtet werden:

- Fehlerhafter Austausch von Lithium Batterien kann zu lebensgefährlichen Explosionen führen.

- Es darf nur der Batterietyp verwendet werden, der auch bereits eingesetzt ist.

### Umweltschutz

Alte Batterien und/oder Boards oder Systeme müssen stets gemäß der in Ihrem Land gültigen Gesetzgebung entsorgt werden.

# 1 Introduction

|                 | The PPC/PowerCoreCPCI-6750 is a high-performance single-board com-<br>puter providing a peripheral CompactPCI interface. It is based on                                                                                                                                                         |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                 | • the microprocessor PowerPC 750                                                                                                                                                                                                                                                                |

|                 | • and on the PCI bus.                                                                                                                                                                                                                                                                           |

| Memory          | Per default the PPC/PowerCoreCPCI-6750 provides one memory module of up to 128 MByte. There are 2 types of memory modules available:                                                                                                                                                            |

|                 | EDO DRAM memory modules                                                                                                                                                                                                                                                                         |

|                 | • and SDRAM memory modules.                                                                                                                                                                                                                                                                     |

|                 | Depending on the memory module installed on the board, the memory capacity may be increased by installing an upper memory module on the (lower) memory module (see section 2.1.1 "Requirements" on page 5).                                                                                     |

|                 | The secondary (L2) cache has a size of up to 1 MByte. The boot flash has a maximum capacity of 2 MByte and the on-board user flash has a maximum capacity of 8 MByte.                                                                                                                           |

| Interfaces      | The PPC/PowerCoreCPCI-6750 includes a peripheral CompactPCI inter-<br>face, PCI bus interfaces, Ethernet interface, and 2 serial I/O ports to pro-<br>vide full single-board computer functionality. The serial I/O ports are<br>available at the front panel via 9-pin Micro D-Sub connectors. |

| CPU Speed       | The PowerPC CPU runs with a minimum frequency of 233 MHz and pro-<br>vides cache snooping support in order to maintain cache coherency.                                                                                                                                                         |

| Real-Time Clock | A real-time clock with on-board battery backup is also available.                                                                                                                                                                                                                               |

#### Specification 1.1

| Table 1                         | Specification of the PPC/PowerCoreCPCI-6750                                                                                                                                                         |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Processor                       | PowerPC 750                                                                                                                                                                                         |

| Shared memory                   | 64-MByte EDO DRAM or 128-MByte SDRAM<br>upgradable to max. 256 MByte                                                                                                                                |

| PMC slots                       | 2 for 32-bit PMC modules<br>I/Os for both PMC modules on CompactPCI connectors J4 and J5                                                                                                            |

| Peripheral CompactPCI interface | PCI-to-PCI bridge                                                                                                                                                                                   |

| PCI interface                   | PPC-to-PCI bridge                                                                                                                                                                                   |

| Ethernet interface              | Ethernet controller<br>10Base-T or 100Base-Tx on front panel, self-negotiating                                                                                                                      |

| 2 serial I/O ports              | RS-232 compatible<br>I/O on front panel                                                                                                                                                             |

| Counters/timers                 | Three 16-bit, programmable                                                                                                                                                                          |

| Boot flash                      | Up to 2 MByte<br>On-board programmable<br>Hardware write protection                                                                                                                                 |

| User flash                      | Up to 8 MByte<br>On-board programmable<br>Hardware write protection                                                                                                                                 |

| RTC/SRAM/battery                | Real-time clock and NVRAM                                                                                                                                                                           |

| Additional features             | Reset and abort key, status LEDs, user LEDs, serial PROM for board configuration, voltage sensors, watchdog timers                                                                                  |

| Firmware                        | PowerBoot                                                                                                                                                                                           |

| Power consumption               | see section 2.1 "Installation Prerequisites and Requirements" on page 5                                                                                                                             |

| Environm. conditions            | see subsection 'Environmental Requirements" on page 8 and table 7<br>"Environmental Requirements of the PPC/PowerCoreCPCI-6750" on<br>page 8                                                        |

| Standards compliance            | CompactPCI Specification PICMG 2.0 R2.1<br>CompactPCI Hot Swap Specification PICMG 2.1 R1.0<br>PCI Local Bus Specification Rev. 2.1<br>IEEE P1386.1/Draft 2.0 - Layers for PCI Mezzanine Cards: PMC |

The PPC/PowerCoreCPCI-6750 is available in several memory and speed options. Consult your local sales representative to confirm availability of specific combinations.

## 1.2 Product Nomenclature

#### Table 2 Nomenclature of the PPC/PowerCoreCPCI-6750

| PPC/PowerCore-6750/yyS-ccc-Llll-z |                                   |  |

|-----------------------------------|-----------------------------------|--|

| 750                               | PowerPC processor type 750        |  |

| yyS                               | DRAM size in MByte, S means SDRAM |  |

| ссс                               | Processor clock frequency in MHz  |  |

| LIII                              | L2 cache capacity in KByte        |  |

| Z                                 | User flash capacity in MByte      |  |

# **1.3 Ordering Information**

The following table is an excerpt from the PPC/PowerCoreCPCI-6750 ordering information at the time of print. Contact your local Force Computers representative for current information.

#### Table 3Excerpt from the Product's Ordering Information

| Product name            | Description                                                                                                     |

|-------------------------|-----------------------------------------------------------------------------------------------------------------|

| PPC/PowerCoreCPCI-6750/ |                                                                                                                 |

| 16-233-L512-4           | PowerPC 750, 16-MByte EDO DRAM, 233-MHz nominal processor frequency, 512-KByte L2 cache, and 4-MByte user flash |

| 64-233-L512-4           | PowerPC 750, 64-MByte EDO DRAM, 233-MHz nominal processor frequency, 512-KByte L2 cache, and 4-MByte user flash |

| 64S-300-L1024-8         | PowerPC 750, 64-MByte SDRAM, 300-MHz nominal processor frequency, 1-MByte L2 cache, and 8-MByte user flash      |

| 128S-300-L1024-8        | PowerPC 750, 128-MByte SDRAM, 300-MHz nominal processor frequency, 1-MByte L2 cache, and 8-MByte user flash     |

| 64S-400-L1024-8         | PowerPC 750, 64-MByte SDRAM, 400-MHz nominal processor frequency, 1-MByte L2 cache, and 8-MByte user flash      |

| Table 3Excerpt from the Product's Ordering Information (cont.) |                                                                                                                            |  |

|----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--|

| Product name                                                   | Description                                                                                                                |  |

| 128S-400-L1024-8                                               | PowerPC 750, 128-MByte SDRAM, 400-MHz nominal processor frequency, 1-MByte L2 cache, and 8-MByte user flash                |  |

| PPC/PowerCore                                                  |                                                                                                                            |  |

| MEM/128U                                                       | User upgradable upper EDO DRAM memory module, 128 MByte                                                                    |  |

| SMEM/128U                                                      | User upgradable upper SDRAM memory module, 128 MByte                                                                       |  |

| Accessories                                                    |                                                                                                                            |  |

| ACC/IOBP/RTB860-E1-120                                         | rear transition board to be used in conjunction with the PMC/860/xx-E1-R module where xx is the processor frequency in MHz |  |

| ACC/IOBP/RTB860-T1-100                                         | rear transition board to be used in conjunction with the PMC/860/xx-T1-R module where xx is the processor frequency in MHz |  |

| 3   | Excerpt from the Product's Ordering Information (cont.) |

|-----|---------------------------------------------------------|

| J 1 | Excer printing intering intering (cont.)                |

# **3** Installation

This chapter provides important information for the installation of the PPC/PowerCoreCPCI-6750.

Before installing the PPC/PowerCoreCPCI-6750, read section "Safety Notes" on page xiii.

## **3.1 Installation Prerequisites and Requirements**

*Note:* Before powering up or plugging the board in, check this section for installation prerequisites and requirements and check the consistency of the current switch setting (see section 3.4 "Switch Settings" on page 17).

#### 3.1.1 Requirements

The installation requires only

- a power supply for 5 V and 3.3 V,

- a fan unit providing an airflow meeting the thermal requirements of the PPC/PowerCoreCPCI-6750,

- and a CompactPCI backplane with P1 and P2 connectors.

Power The PPC/PowerCoreCPCI-6750 provides a limited current at the PMC supply pins. The maximum current depends on:

- the CPU type and frequency

- and the installed memory modules.

Typical power requirements of the board are given in the following table:

| Table 1 | Typical Power Requirements of the Board incl. M       | Typical Power Requirements of the Board incl. Memory Module |       |  |

|---------|-------------------------------------------------------|-------------------------------------------------------------|-------|--|

|         | Board with lower memory module but without PMC module | +5 V                                                        | 3.3 V |  |

|         | PPC/PowerCoreCPCI-6750/16-233-L512-4                  | 1.9 A                                                       | 1.8 A |  |

|         | PPC/PowerCoreCPCI-6750/64-233-L512-4                  | 2.2 A                                                       | 1.9 A |  |

|         | PPC/PowerCoreCPCI-6750/64S-300-L1024-8                | 1.2 A                                                       | 2.2 A |  |

|         | PPC/PowerCoreCPCI-6750/128S-300-L1024-8               | 1.2 A                                                       | 2.2 A |  |

|         | PPC/PowerCoreCPCI-6750/64S-400-L1024-8                | 1.4 A                                                       | 1.9 A |  |

|         | PPC/PowerCoreCPCI-6750/128S-400-L1024-8               | 1.4 A                                                       | 1.9 A |  |

Memory Modules Per default the shared memory of the board is provided by one (lower) memory module directly located on the board. The following 2 types of memory modules are available:

- EDO DRAM memory module

- and SDRAM memory module.

If your board is equipped with one of the following lower memory modules, you may increase the capacity of the memory by installing an additional appropriate (upper) memory module on top of the lower one:

- 64-MByte EDO DRAM memory module

- 64- or 128-MByte SDRAM memory module.

All other memory modules per default installed on the board, for example the 16-MByte EDO DRAM memory module, cannot be upgraded.

When installing or uninstalling a memory module, observe the following safety notes:

The PPC/PowerCoreCPCI-6750 may be equipped only with memory modules qualified by Force Computers. Otherwise the board or connected components may be damaged.

Before installing or uninstalling the memory module turn off the power, since the memory modules do not provide hot-swap functionality.

Do not place an EDO DRAM memory module on top of an SDRAM memory module or vice versa.

Out of the comprehensive list of possible configurations the memory configurations shown in the following table have been qualified.

|                             | PPC/PowerCore |           |

|-----------------------------|---------------|-----------|

|                             | MEM/128U      | SMEM/128U |

| PPC/PowerCoreCPCI-6750/64   | x             | _         |

| PPC/PowerCoreCPCI-6750/64S  | _             | х         |

| PPC/PowerCoreCPCI-6750/128S | _             | X         |

#### Table 2 Qualified Memory Module configurations

The upgrading instructions are shipped together with the memory modules: see the respective *Memory Module Installation Guide*.

When installing an upper memory module on the lower memory module installed per default on the board, you have to consider the power consumption. In this case add

- the power consumption of the board including lower memory module (see table 1 "Typical Power Requirements of the Board incl. Memory Module" on page 10)

- and the max. power consumption drawn by the upper memory module (see table 3 "Max. Power Consumption of the Upper Memory Modules").

#### Max. Power Consumption of the Upper Memory Modules

| PPC/PowerCore | 3.3 V |

|---------------|-------|

| MEM/128U      | 0.1 A |

| SMEM/128U     | 0.2 A |

PMC

Table 3

The PPC/PowerCoreCPCI-6750 provides 2 PMC slots which can be used to install PMC modules based on the PCI bus architecture. The maximum permissible power consumption of each PMC module is 7.5 W.

Before installing or uninstalling a PMC module turn off the power, since the PMC modules do not provide hot-swap functionality.

| Environmental | The following table summarizes the environmental requirements of the |

|---------------|----------------------------------------------------------------------|

| Requirements  | PPC/PowerCoreCPCI-6750.                                              |

Table 4

Environmental Requirements of the PPC/PowerCoreCPCI-6750

|                | Operating                        | Non-operating                    |

|----------------|----------------------------------|----------------------------------|

| Temperature    | $0^{\circ}$ C to +55°C           | -40°C to +85°C                   |

| Forced airflow | 300 LFM (linear feet per minute) | -                                |

| Temp. change   | +/- 0.5°C/min                    | +/- 1°C/min                      |

| Rel. humidity  | 5% to 95% noncondensing at +40°C | 5% to 95% noncondensing at +40°C |

| Altitude       | -300 m to +3,000 m               | -300 m to +13,000 m              |

The environmental conditions must be tested and proven in the used system configuration. These conditions refer to the surroundings of the board within the user environment. Operating temperatures refer to the temperature of the air circulating around the board and not to the actual component temperature. To meet the operating conditions, forced airflow is required at the heat sink of the CPU and at the top side of the board.

#### 3.1.2 Terminal Connection

For the initial power-up, a terminal can be connected to the left 9-pin MicroD-Sub connector, which is located at the front panel (see section 3.7 "Serial I/O Ports" on page 20).

#### 3.1.3 Location Overview

The figure 1 "Location diagram of the PPC/PowerCoreCPCI-6750 (schematic)" on page 13 shows the location of the important PPC/PowerCoreCPCI-6750 components. Depending on the board type it might be that your board does not include all components named in the location diagram.

Page 13

#### 3.1.4 Upgrading the PPC/PowerCoreCPCI-6750

| Memory Module | Depending on the (lower) memory module which is per default installed<br>on the PPC/PowerCoreCPCI-6750, it is possible to increase the memory<br>capacity of the board by installing an upper memory module on top of the<br>(lower) memory module.<br>For detailed information on the memory modules, see |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | <ul><li>section 3.1 "Installation Prerequisites and Requirements" on page 9</li><li>and the respective <i>Memory Module Installation Guide</i>.</li></ul>                                                                                                                                                  |

| PMC Module    | The PPC/PowerCoreCPCI-6750 provides 2 PMC slots. The PMC slots can be used to install PMC modules based on the PCI bus architecture. For detailed information on the PMC modules, see                                                                                                                      |

|               | • section 3.1 "Installation Prerequisites and Requirements" on page 9                                                                                                                                                                                                                                      |

• and section 3.12 "PMC Slots" on page 25.

## 3.2 Installing Under Hot-Swap Conditions

The PPC/PowerCoreCPCI-6750 is a full hot-swap board. This covers board support in the following situations:

- The basic purpose of hot-swap support is to allow the board to be installed and uninstalled in a powered system without adversely affecting system operation. This is done for repairing faulty boards or reconfiguring a system.

- Additionally, hot-swap support provides programmatic access to hotswap services allowing system reconfiguration and fault recovery to take place without system down time and with minimum operator interaction.

- Finally, hot-swap support allows the system to isolate faulty boards so that a system can continue operating in case of failure possibly with reduced capability. This is especially useful in the area of high-availability applications, although typically other features may be in a prominent role to the user of high-availability applications.

The PPC/PowerCoreCPCI-6750 can be used in non hot-swap systems, basic hot-swap systems, full hot-swap systems, and high-availability systems. The PPC/PowerCoreCPCI-6750 provides the signals ENUM# and HEALTHY# for host or hot-swap-controller (HSC) notification, 4 control and status bits concerning hot-swap conditions, a hot-swap switch (integrated in the lower handle), and a blue LED to interface with the operator.

- After installing or before uninstalling the PPC/PowerCoreCPCI-6750 in a powered system, the interrupt ENUM# is generated and passed to the system board of the CompactPCI system to indicate a service request.

- A set of 4 control and status bits on each board allows the host software to determine the source of the ENUM# signal and control the hot-swap LED.

- The hot-swap switch allows the operator to indicate the intention to uninstall the board. The PPC/PowerCoreCPCI-6750 implements the hot-swap switch in the lower handle of the front panel.

- The blue hot-swap LED indicates that it is allowed to uninstall the board.

*Note:* If hot-swap is supported by the system, at least the system documentation includes installation guidelines how to install or uninstall boards under hot-swap conditions. The system documentation includes both the hardware documentation and the software documentation. The hardware documentation covers chassis and installed boards - in CompactPCI hot-swap terms the platform. The software documentation covers the operating system, possibly additional drivers, and applications - in CompactPCI hotswap terms all which makes a platform a system. Therefore: Refer to the documentation of all installed boards and to the system documentation. Never install or uninstall the PPC/PowerCoreCPCI-6750 in a system under hot-swap conditions unless the system documentation explicitly includes appropriate guidelines for these 2 tasks.

- Installing and<br/>Uninstalling1. Start uninstalling the board by checking all installed boards for steps<br/>that you have to take before removing a board from a powered sys-<br/>tem.

- 2. Take those steps.

- 3. Open the lower front-panel handle to indicate removal.

- 4. Wait until the hot-swap LED turns blue.

*Note:* As long as the hot-swap LED is off, the board is in normal operation and must not be removed.

- 5. Remove the board from the powered system.

- 6. Reconfigure the board according to your needs or replace it by another board.

- 7. Start installing the reconfigured board or the replacement board by checking all boards for steps that you have to take before installing a board under hot-swap conditions:

- Check the boards which are installed from the front side of the backplane.

- Check the installation configuration of the rear I/O for the slot in which the board is going to be plugged in.

- 8. Take those steps.

- 9. Finally insert the board into the powered system.